ARTIGO ORIGINAL

MELO, Telmo Gabriel de Jesus Torres de [1], ARAÚJO, Jalberth Fernandes de [2]

MELO, Telmo Gabriel de Jesus Torres de. ARAÚJO, Jalberth Fernandes de. Influência dos parâmetros do CMOS no dispositivo BiCMOS 0,13µm. Revista Científica Multidisciplinar Núcleo do Conhecimento. Ano 04, Ed. 10, Vol. 07, pp. 80-95. Outubro de 2019. ISSN: 2448-0959, Link de acesso: https://www.nucleodoconhecimento.com.br/engenharia-eletrica/influencia-dos-parametros

RESUMO

Os parâmetros são, no âmbito da microeletrônica, de fundamental importância para uma correta modelagem e estudo do componente, sendo que nem sempre é uma tarefa trivial. Visto isso, neste documento são descritas as atividades desenvolvidas pelo aluno Telmo Gabriel de Jesus Torres de Melo no Laboratório de Instrumentação e Metrologias Científicas. Esse artigo realizado teve como finalidade confeccionar uma lista que facilite a identificação dos diferentes tipos de parâmetros que influenciam no CMOS quando está inserido na topologia BiCMOS 0,13µm. Essa lista é focada nos principais parâmetros que são passíveis de simulação computacional com BiCMOS aplicado a tecnologia RFID. A necessidade desse catálogo é suprir o problema que os colaboradores do laboratório tinham, pois, a equipe nem sempre tinha o completo domínio dos parâmetros necessários para realizar uma simulação.

Palavras-Chave: Análise de parâmetros, BiCMOS, CMOS, microeletrônica, lista.

INTRODUÇÃO

A análise dos parâmetros é de grande importância para a Engenharia, pois permite realizar o dimensionamento, projeto ou análise de um sistema de forma a correta. No caso da Engenharia Elétrica, torna-se de fundamental importância o conhecimento dos principais parâmetros utilizados em qualquer projeto técnico, visto que o mal dimensionamento influência no desempenho de qualquer sistema. Não sendo diferente na eletrônica, onde a identificação dos parâmetros dos dispositivos micro ou nano eletrônicos é um trabalho fundamental para a correta utilização e/ou dimensionamento do dispositivo.

No âmbito dos dispositivos microeletrônicos BiCMOS, o fabricante ao vender um equipamento insere uma folha de dados chamada de datasheet, que possui todos os parâmetros, gráficos e características técnicas necessárias para a utilização do BiCMOS. Essa folha de dados possui a especificação de desempenho do dispositivo aos mais variados tipos de funcionamento, como tensão de operação para diferentes temperaturas e corrente. Os resultados demonstrados são feitos a partir de condições especificadas por órgãos internacionais, como JEDEC (Joint Electron Tube Engineering Council), que impõem técnicas e normas para realizar testes que geram os resultados do datasheet (JEP143, 2001).

Todavia, o datasheet de BiCMOS é muitas vezes extenso, tornando a localização de parâmetros funcionais, como capacitância do óxido do CMOS, um componente do BiCMOS, uma tarefa demorada até mesmo para usuários experientes. Essa demora pode ser entendida como um maior tempo exigido para realizar um projeto via software. Entretanto, caso um parâmetro seja negligenciado, como considerar um valor errôneo para a capacitância do óxido do CMOS, a simulação poderá divergir da resposta correta.

Assim, esse artigo engloba um compilado de informações sobre os principais parâmetros do CMOS que influenciam no desempenho do dispositivo BiCMOS na aplicação de RFID, com a finalidade de minimizar o tempo de análise e concepção da simulação, otimizando tempo de realização de um projeto. O foco desse é expor os principais parâmetros de fabricação do CMOS sob a tecnologia BICMOS 0.13 µm, fazendo um paralelo com as tecnologias mais atuais e comprovando os resultados com simulações no software OrCAD/PSpice.

O Estágio Supervisionado foi realizado no Laboratório de Instrumentação e Metrologias Científicas, LIMC, que fica localizado no campus da Universidade Federal de Campina Grande. A criação do LIMC se deu em 1997, em um acordo internacional bilateral da CAPES/COFEPUC com a Ecole Nationale Supérieure des Télécommunications, hoje chamada de Télécom ParisTech.

O ambiente do laboratório é formado por seis salas de estudo e equipamentos e duas salas para cada um dos professores coordenadores. Cada sala de estudo possui computadores para os colaboradores além de equipamentos como osciloscópio, multímetro e gerador de sinal. Atualmente a equipe do LIMC conta com 18 graduandos, 3 mestrandos e 9 doutorandos.

Dentre as atividades desenvolvidas no LIMC, destaca-se aquelas com ênfase em eletrônica, sendo o foca da linha de pesquisa em aplicações de sensores termorresistivos, concepção de circuitos integrados, instrumentação eletrônica, sensores RFID e sistemas inteligentes.

OBJETIVOS

O objetivo geral do trabalho é catalogar os principais parâmetros do CMOS na tecnologia BiCMOS 0.13 µm passíveis de simulação nos principais softwares existentes. Os objetivos específicos são divididos em:

- Catalogar os principais parâmetros do CMOS que mais influenciam no BiCMOS;

- Comparar a tecnologia BiCMOS 0.13 µm com tecnologias mais modernas.

REFERENCIAL TEÓRICO

A tecnologia BiCMOS é a combinação do transistor de junção bipolar (TBJ) e CMOS em um único circuito integrado. Mantendo os benefícios do Bipolar e do CMOS, o BiCMOS é capaz de obter circuitos integrados de produção elevada com um desempenho anteriormente inatingível, comparada o CMOS e TBJ. A tecnologia CMOS mantém uma vantagem face a Bipolar no consumo de energia, margens de ruído, densidade de encapsulamento e a capacidade de integrar grandes funções complexas com alto rendimento. A tecnologia bipolar tem vantagens sobre o CMOS na velocidade de comutação, na corrente por unidade de área, no desempenho de ruído, na capacidade analógica e na velocidade de resposta E/S (entrada e saída). A capacidade de conciliar a alta velocidade de comutação e baixo consumo e dissipação de energia, qualidades do CMOS e TBJ, faz com que a tecnologia BiCMOS seja uma escolha sensata para o projetista, caso a especificação do projeto seja o alto desempenho (BAKER, 2001).

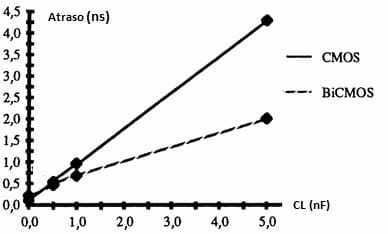

Uma análise comparativa com o BiCMOS pode ser realizada no ponto mais crítico da topologia CMOS, que é a velocidade de resposta frente a capacitância da carga. No primeiro caso, conforme o gráfico da Figura 1, foi variado a capacitância da carga (CL) e aferido a resposta do CMOS e BiCMOS, sendo ambos de mesma largura, 1µm, e submetidos a mesma temperatura, 25 ºC (ALVAREZ, 2003).

Figura 1 – Gráfico do tempo de resposta versus variação da carga para o CMOS e BiCMOS.

Observa-se que a inclinação da curva que representa o crescimento do atraso em face o aumento da capacitância da carga para a tecnologia CMOS é muito maior que o do BiCMOS. Esse menor atraso é uma consequência direta de se possuir o TBJ em sua composição, visto que o TBJ é menos sensível a variação da capacitância.

Historicamente, a topologia BiCMOS foi desenvolvida para ser um CMOS com velocidade ou um TBJ com menor dissipação de energia. Entretanto, como resultado da evolução, o BiCMOS moderno é baseado tanto no processo do TBJ como do CMOS, resultando em uma performance geral acima das duas topologias, porém com uma performance um pouco abaixo se considerado operações extremas, como tempo de resposta de uma porta lógica AND feita sob topologia TBJ com a entrada variando a 200 GHz. Essa versatilidade foi aproveitada usando processo arquitetural modular (disposição no chip) e com a fácil inserção de elementos não voláteis, como poli silício, tornando a implementação de estruturas complexas, como SRAM, extremamente rápidas, sendo que estas eram dominadas pelo TBJ (RATNAKUMA, 1990).

A maior complexidade do chip BiCMOS frente ao TBJ e CMOS resulta em um processo de fabricação 30% mais caro que os já consolidados e tradicionais CMOS e TBJ. Essa desvantagem mercadológica condiciona essa tecnologia ao fator limitante que é o quesito financeiro. Além disso, outro ponto negativo que muitas vezes não é levado em consideração é a necessidade de uma maior quantidade de pré-requisitos e especificações para controle de qualidade, visto que o BiCMOS possui um TBJ e CMOS em um único dispositivo. (CRESSLER, 2003).

Na técnica do projeto de BiCMOS, o projetista sempre almeja otimizar a velocidade de processamento, a demanda de energia e a rejeição ao ruído, independentemente qual a seja a aplicação do BiCMOS. Visto isso, é necessário fazer uma listagem de quais parâmetros contribuem mais para a velocidade, consumo e rejeição ao ruído (ALVAREZ, 2003).

INFLUÊNCIA DOS PARÂMETROS DO CMOS NO BICMOS

A análise dos parâmetros do CMOS é de fundamental importância para a correta modelagem do BiCMOS. Para isso, observa-se uma variada gama de parâmetros que descrevem os mais variados tipos de aplicação do BiCMOS. Dessa maneira, percebe-se que existem muitos parâmetros que pouco influenciam, ou somente influenciam em condições de operações extremas, como a temperaturas elevadas, o que não é o foco de pesquisa do LIMC. Visto isso, para estudos laboratoriais, como o realizado no Laboratório de Instrumentação e Metrologias Científicas, faz-se necessário identificar qual desses parâmetros do CMOS realmente tem mais influência e contribuição para a resposta final do BiCMOS.

A dissipação de energia e o grau de insensibilidade ao ruído do BiCMOS é determinado pela tensão de limiar (threshold). A tensão de limiar é o potencial necessário aplicado na porta para que o canal comece a aparecer, usualmente entre 300 mV e 500 mV (RAZAVI, 2010). Aumentar a tensão de limiar do CMOS, ocorre a redução da dissipação de energia e o aumento da insensibilidade ao ruído, todavia, o mesmo aumento da tensão de limiar acarreta uma degradação maior da velocidade de operação máxima suportada (ALVAREZ, 2003).

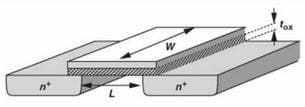

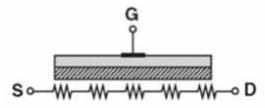

A espessura do óxido do CMOS (???), mostrado na Figura 2, é um parâmetro que afeta o funcionamento do CMOS e, consequentemente, BiCMOS. À medida que ??? aumenta, a capacitância entre a porta e o substrato de silício diminui. Portanto, nota-se que resulta em menor carga na porta e, em consequência, em uma menor densidade de elétrons no canal (RAZAVI, 2010). Desta forma, o dispositivo apresenta uma resistência em condução mais alta e, para uma dada tensão de porta, produz uma menor corrente de dreno ou tensão de dreno. Por este motivo, a indústria de semicondutores continua a reduzir a espessura de oxido da porta. Embora tanto o comprimento como a espessura do óxido afetem o desempenho do CMOS, apenas o primeiro está sob controle no projetista, isto é, o comprimento pode ser especificado no layout e a última, por sua vez, é definida durante a fabricação e permanece constante em todos os transistores de uma dada geração da tecnologia.

Figura 2 – Representação física dos parâmetros do MOS.

A partir do parâmetro ???, deriva-se um outro parâmetro de fundamental importância, a capacitância do óxido ???. Esta é a principal capacitância parasita do dispositivo CMOS. A dimensão da porta do CMOS, mostrado com W e L na Figura 3, influência no tamanho do canal e, consequentemente, na velocidade, ruído e gasto de energia do BiCMOS. A medida que W aumenta, a largura do canal também aumenta, o que reduz a resistência entre fonte e dreno. De outra perspectiva, um dispositivo mais largo pode ser visto como dois transistores mais estreitos em paralelo, produzindo uma corrente de dreno alta (BOYLESTAD). Podemos, então, concluir que W deve ser maximizada, mas também devemos notar que a capacitância de porta total aumenta com W, o que pode vir a limitar a velocidade do circuito. Ou seja, a largura de cada dispositivo no circuito deve ser escolhida com muito cuidado de acordo com a especificações de projeto (RAZAVI, 2010).

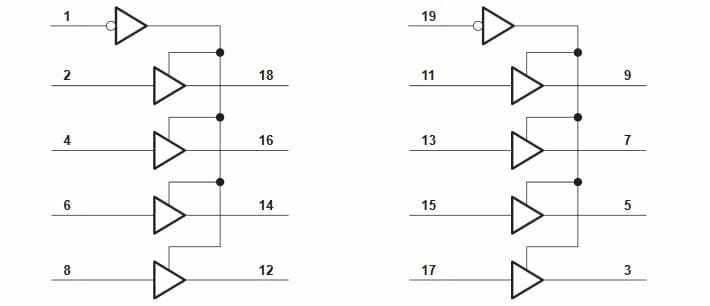

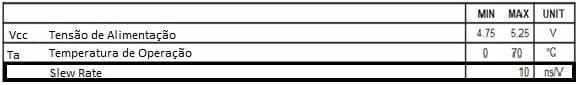

No ponto de vista da operação, é importante que, durante a operação, o CMOS do arranjo do BiCMOS tenha uma resposta rápida e efetiva da saída em relação a variação da tensão de entrada, o chamado slew rate. Nos BiCMOS, que possuem a propriedade do TBJ de uma velocidade elevada de resposta na saída, esse valor deve ser o menor possível para cada volt aplicado, ou seja, a variação de tempo para a saída variar em relação a entrada deve-se ser, idealmente, zero. Assim, instantaneamente após variar a tensão a saída daria uma resposta. Tomando como exemplo o circuito de buffers feito com BiCMOS CD74FCT244 representado na Figura 3(a), da Texas Instrument, o valor do slew rate pode ser mostrado no Quadro 1.

Figura 3 – Circuito equivalente do CI CD74FCT244.

Quadro 1: Tabela de condições nominais de operação do CD74FCT244.

Do ponto de vista arquitetural do dispositivo, é importante observar a influência do encapsulamento do CMOS no comportamento do BiCMOS. Atualmente há uma variedade de novos encapsulamentos no mercado, deixando os clássicos TO220, TO247 e D2PAK de serem as únicas opções para os desenvolvedores. O desenvolvimento destes novos invólucros é acompanhado pela melhoria das características dinâmicas dos MOSFET, permitindo a redução de dissipadores ou até a mesma dissipação na própria placa de circuito impresso. Cada encapsulamento possui benefícios e contrapartidas, como resistência do encapsulamento, indutância característica e a resistência térmica. A Tabela 1 mostra a resistência e impedância parasita de diferentes tipos de encapsulamento.

Tabela 1: Relação de elementos parasitas com o tipo de encapsulamento.

| Resistência Parasita(mΩ) | Impedância Parasita(nH) | |

| S0-8 | 1,0 | 1,5 |

| CopperStrap | 1,0 | 0,8 |

| PowerPak | 0,8 | 0,8 |

| DirectFET | 0,15 | <0,1 |

Fonte: Datasheet Infineon Technologies (2018).

O método de tomada de decisão na escolha do encapsulamento resulta em benefícios que implicam em custo extra para o dispositivo.

Do ponto de vista da resistência, um CMOS pode atuar como um resistor variável entre os terminais da fonte e dreno, conforme a Figura 4, sendo a resistência controlada pela tensão. O aumento da tensão na porta é diretamente correlacionado com a densidade de elétrons que flui pelo canal, ou seja, a implicação do aumento da tensão na porta é a elevação da densidade de elétrons no canal, reduzindo a resistência em condução (BOYLESTAD, 2013). Outro fator que influencia a o comportamento do BiCMOS é a resistência do canal é o comprimento do canal do CMOS, onde o aumento deste aumenta também a resistência de condução. Portanto, é desejável minimizar o comprimento do canal para obter correntes de dreno intensas – uma tendência importante no desenvolvimento da tecnologia MOS (RAZAVI, 2010).

Figura 4 – Resistência entre os terminais do dreno e fonte.

METODOLOGIA

Para comprovar o que foi demonstrado no âmbito teórico, foram realizadas simulações no software PSpice para corroborar a real influência dos parâmetros no desempenho do circuito, com o CMOS sendo aplicado em diferentes tipos de circuitos.

O programa PSPICE (ORCAD) é um simulador digital de circuitos eletrônicos, que emula os comportamentos de um circuito real. Deste modo ele permite fazer todos os testes do projeto, certificando que o projeto proposto está correto e possa ser implementado. O simulador de circuitos PSPICE foi criado pela empresa Microsim , e em poucos anos já era o simulador de circuitos eletrônicos mais utilizado do mundo. Cada ano que passava, uma nova versão era desenvolvida. A Microsim desenvolveu seu software até a versão 8.0, com o nome de Microsim PSPICE. O software PSPICE foi vendido para a empresa Cadence Design Systems, que por sua vez mudou o nome para ORCAD. A primeira versão do software ORCAD é a versão 9.0 e a última da Microsim é a 8.0, confirmando a linhagem do software.

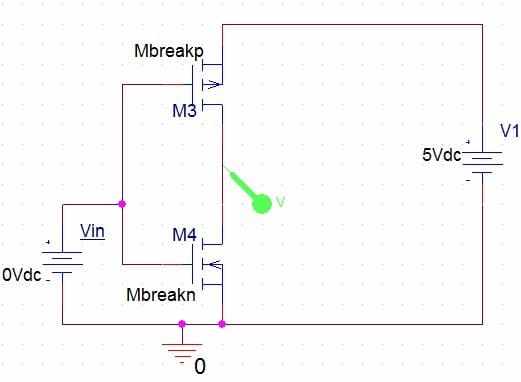

Na simulação realizada, o circuito simulado foi o de um CMOS inversor, conforme a Figura 5. O CMOS foi simulado a partir de um MOS tipo N e outro tipo P em simetria complementar, ou seja, compartilhando a porta. Uma fonte de tensão DC foi acoplada e, para plotar o gráfico, a fonte variou de 0 V a 5 V com um passo incremental de 0.05 V.

SIMULAÇÃO E RESULTADOS

A avaliação dos parâmetros do CMOS é de fundamental importância para a determinação dos resultados em qualquer topologia que o CMOS esteja inserido. Visto isso, foi realizado simulações no software PSpice para corroborar a real influência dos parâmetros na resposta final do circuito, com o CMOS sendo aplicado em diferentes tipos de circuitos.

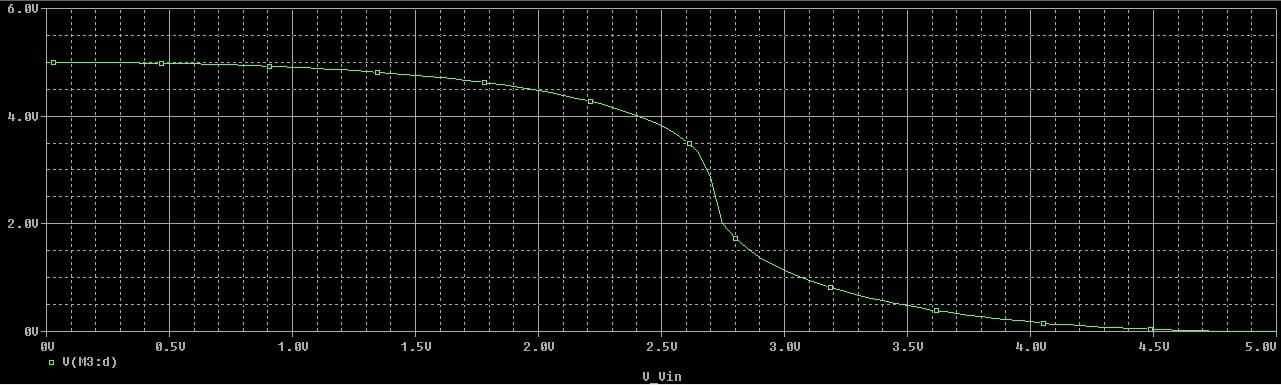

Na primeira simulação realizada, o circuito simulado foi o de um CMOS inversor, conforme a Figura 5. O CMOS foi simulado a partir de um MOS tipo N e outro tipo P em simetria complementar, ou seja, compartilhando a porta. Uma fonte de tensão DC foi acoplada e, para plotar o gráfico, a fonte variou de 0 V a 5 V com um passo incremental de 0.05 V.

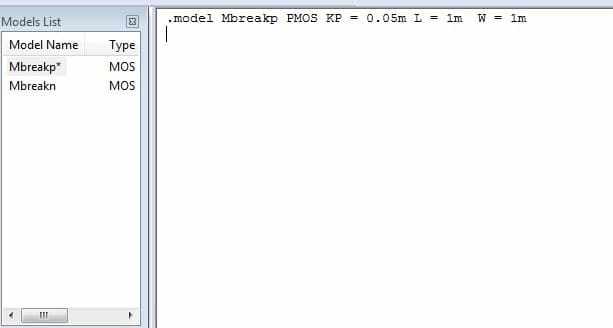

No âmbito dos parâmetros, alterado as constantes ??? e ? a partir do parâmetro do software KP, sendo KP a multiplicação das duas constantes. Assim, uma nova linha de instrução foi adicionada no software, conforme a Figura 6 mostra e foi simulado. O resultado da simulação pode ser aferido na Figura 7.

Figura 5 – Circuito equivalente para o inversor.

Figura 6 – Linha de código adicional com os parâmetros.

Figura 7 – Saída do inversor.

Observa-se que a curva resultando do inversor possui um ponto de simetria no eixo y em 2,5 V e sendo essa resposta esperada, visto que o CMOS tipo N e tipo P possuem mesmo parâmetros na simulação. Outro ponto de destaque é que a transição de nível lógico não se dá de forma abrupta em 2,5 V. Isso se deve ao fato de estarmos usando um número finito de pontos no DC Sweep. No caso ideal, a transição deve ser perfeitamente vertical, mas apenas um ponto dos 101 pontos configurados na simulação irá corresponder a essa transição. Deve-se salientar que inversores reais possuem essa curva simulada, pois os mesmos são feitos com componentes reais e não ideais.

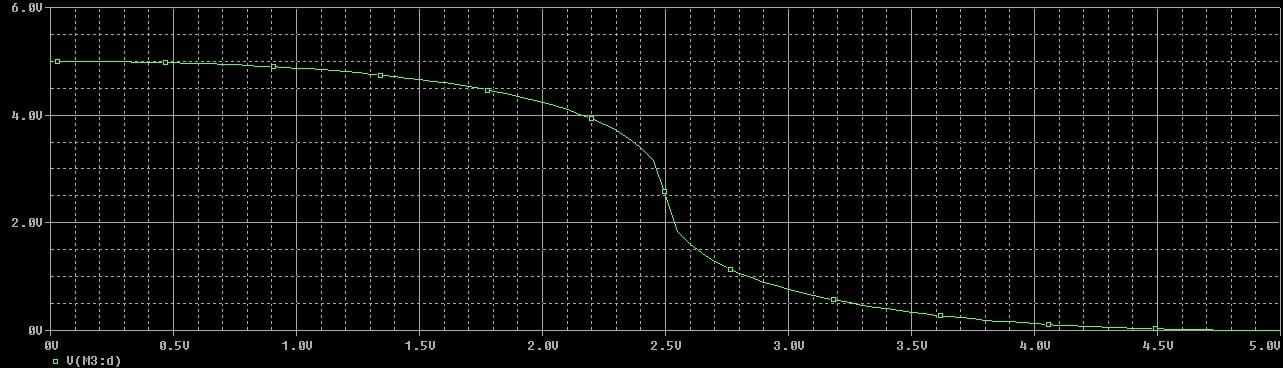

Alterando qualquer um dos parâmetros analisados em apenas um dos MOSFET acarretará em uma curva com um comportamento antissimétrico em relação ao ponto 2,5

V. Refazendo a simulação variando KP do MOSFET tipo P para 0.2m e mantendo o KP do MOSFET tipo N em 0.5, obtemos uma onda antissimétrica, conforme a Figura 8.

Figura 8 – Saída do inversor para diferentes KP.

É importante observar que o ponto de inflexão de curva acontece agora entre 1.8 V e 2.0 V, 0.6 V a menos que a simulação anterior, devido a variação de parâmetros dos MOSFET utilizados. Observa-se também que a curva possui uma queda mais acentuada na margem inferior.

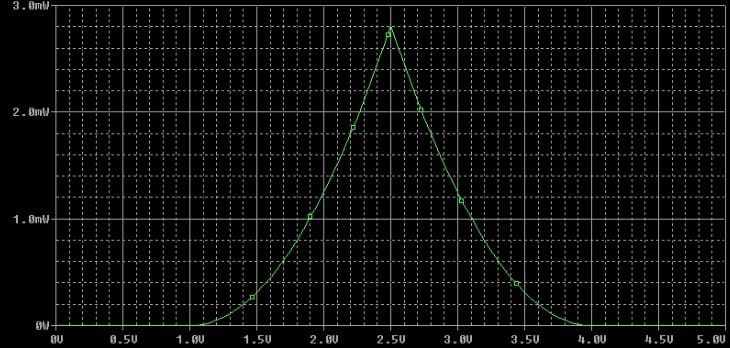

Do ponto de vista da dissipação de potência, ambos os casos de simulação possuem o mesmo pico no momento da transição do nível lógico, mostrando que enquanto não acontece o chaveamento, o dispositivo não possui quase nenhum gasto energético. A Figura 9 mostra a curva de potência em função da tensão para o caso dos parâmetros iguais.

Figura 9 – Potência dissipada no inversor.

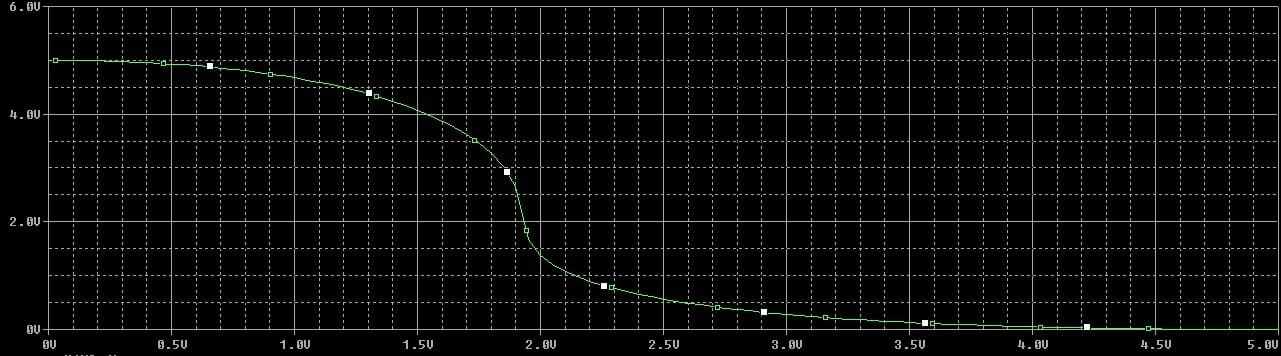

Para a variação do comprimento L, foi plotada a curva do inversor mantendo todos os outros parâmetros do software iguais, resultando na curva apresentada na Figura 10. Os valores de L adotado para os CMOS foi, respectivamente 0.13 µm e 0.18 µm, mostrando o resultado caso o projetista negligenciasse o parâmetro L.

Figura 10: Curva resultante para o inversor CMOS com L1 = 0.13 µm e L2 = 0.18 µm.

Sobre o momento de transição do nível lógico alto (+5 V) para o baixo (0 V), é importante observar que o ponto de inflexão de curva acontece agora 2,8 V, 0,3 V a mais que o ideal. Além disso, percebe-se uma diferença no momento da transição do nível lógico das duas tecnologias, onde perto do momento de transição, em 1,8 V, a curva do CMOS na topologia 0.13 µm é mais abrupta que o CMOS na topologia 0.18 µm.

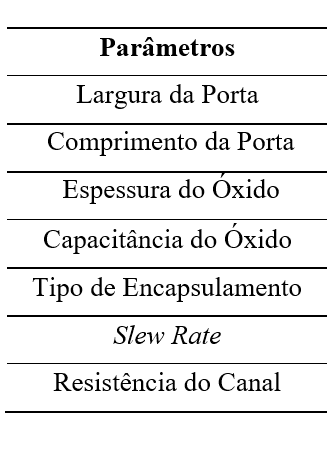

Com base na simulação e na pesquisa teórica, foi-se realizado uma tabela, Tabela 2, que indica quais os principais parâmetros do CMOS que, ao sofrer variação, mais influenciam no comportamento final do BiCMOS. O parâmetro slew rate dessa tabela não é mensurável via software, entretanto, esse parâmetro é resultado de combinações de outros parâmetros já listados.

Tabela 2: Relação de parâmetros analisados.

COMPARAÇÃO COM OS BICMOS ATUAIS

O BiCMOS na tecnologia de 0.13 µm foi desenvolvido pela IBM em 2003 e representa a terceira geração tecnológica de BiCMOS comerciais. Essa topologia é feita a partir de uma liga de Silício e Germânio que possibilita uma largura de canal pequena e resposta do circuito eficiente. No escopo do transistor de junção bipolar, a tecnologia BiCMOS 0.13 µm diverge dos tradicionais TBJ e utiliza o HBT (Heterojunction Bipolar Transistor), que é um TBJ com uma um semicondutor diferente (heterogêneo) para cada junção existente (CRESSLER, 2003).

Atualmente, a tecnologia comercial de BiCMOS está em 14 nm de largura e é aplicada em processadores de última geração, como o Ryzen Threadripper da AMD ou i9 7900-X da Intel. Além disso, com a demanda constante da processamento de microondas como de transmissão de dados via Wi-Fi, comunicações óticas e radares militares, coloca o BiCMOS na vanguarda da tecnologia e investimento.

Com essa espessura de canal, observa-se que vários componentes do BiCMOS possuem características divergentes comparado com o BiCMOS 0.13 µm, como o aumento da resistência da resistência do óxido em frequências elevadas (CHEVALIER, 2015). Além disso, a modelagem dos componentes do BiCMOS fica bem mais rebuscada, saindo do domínio da física de semicondutores para a física quântica.

CONCLUSÃO

A análise dos parâmetros do CMOS é de fundamental importância para a correta análise do BiCMOS. Nessa conjuntura, o BiCMOS é um dispositivo que é composto de CMOS e TBJ, possuindo as características de ambos, logo, a grande maioria dos parâmetros do BiCMOS são herdados dos dispositivos que o compõem, tornando assim de grande valia. Essa vantagem é primordial para aplicações em RFID, micro-ondas e aplicação na indústria automobilista (radar).

Pode-se concluir, com esse artigo a influência dos parâmetros ???, dimensões do canal, tipo de encapsulamento e slew rate, que interferem no comportamento do CMOS e, consequentemente, no comportamento do BiCMOS. As simulações no software PSpice corroboram a influência dos parâmetros, visto que, com apenas a variação de um único parâmetro do CMOS, ocasionou na mudança completa da resposta final do circuito.

REFERÊNCIAS

AVENIER G. “0.13 SiGe BiCMOS technology for mm-wave applications”, Proc.

BCTM, pp. 89-92, 2008-Oct.

BAKER, J. “CMOS, Circuit Design, Layout and Simulation”. 3 ed. John Wiley & Sons, Inc., Hoboken, New Jersey, 2010.BOYLESTAD, R; NASHELSKY, L. “Dispositivos Eletrônicos e Teoria de Circuitos”. Rio de Janeiro: Prentice-Hall do Brasil Ltda., 2001.

CHEVALIER, P. et al., “Low-Cost Self-Aligned SiGeC HBT Module for HighPerformance Bulk and SOI RFCMOS Platforms”, IEDM Technical Digest, pp. 983986, 2005.

CHEVALIER, P.; AVENIER, G.; CANDERLE, E.; MONTAGNE, A.; RIBES, G.; & VU, V. T. Nanoscale SiGe BiCMOS technologies: From 55 nm reality to 14 nm opportunities and challenges. 2015 IEEE Bipolar/BiCMOS Circuits and Technology Meeting – BCTM, 2015.

CRESSLER, J. “ Fabrication of SiGe HBT BiCMOS Technology”. Atlanta: CRCPress, 2003.

LAURENS, M. “A 150 GHz fT/fMAX 0.13 μm SiGe:C Technology”, BCTM Proceedings, pp. 199-202, 2003.

POURCHON, F. “From measurements to intrinsic device characteristics: Test structures and parasitic determination”, Proc. BCTM, pp. 232-239, 2008-Oct.

RAZAVI, B. Fundamentos de Microeletrônica. 1. ed. Rio de Janeiro: LTC, 2010.

RÜCKER, H. “Half-Terahertz SiGe BiCMOS Technology”, SiRF Proceedings, pp. 133-136, 2012.

SEDRA, A. S.; SMITH, K.C. Microelectronic Circuits. 6. ed. Oxford: Oxford University Press Inc., 2013.

VOINIGESCU, S. P; AROCA, R.; TANG, K.; NICOLSON, S.; Laskin, E.; Khanpour, M; Yau K.; TOMKINS, A.; CHALVATZIS, T.; DICKSON, T. O.; HART,A. “Why Moore’s law and scaling work for mm-wave VCOs and PLLs”, Workshop on Advanced PLL Architectures for Embedded SoCs RFIC Symp., 2008-Jun.

[1] Pós-graduando em Engenharia de Segurança do Trabalho pela Faculdade de Tecnologias e Ciências. Engenheiro Eletricista pela Universidade Federal de Campina Grande.

[2] Doutorado em Engenharia Elétrica; Mestrado em Engenharia Elétrica; Graduação em Engenharia Elétrica.

Enviado: Setembro, 2019.

Aprovado: Outubro, 2019.